# 8051 Microcontroller

### 8051 Features

- 8 bit CPU with registers A and B

- 16 bit program counter (PC) and data pointer (DPTR)

- 8 bit program status word (PSW)

- 8 bit stack pointer

- Internal ROM of 0(8031) to 4K(8051)

- Internal RAM of 128 Bytes

- 4 register banks 00-1f

- 16bytes(bit addressable) 20-2f

- 80 bytes of general purpose data memory 30-7f

- 32 I/O pins arranged as four8 bit ports (P0± P3)

- 2 16-bit timer/counters: T0 and T1

- Full duplex serial data receiver/transmitter: SBUF

- Control registers: TCON, TMOD, SCON, PCON, IP and IE

- 2 external and 3 internal interrupt sources

- Oscillator and clock circuits

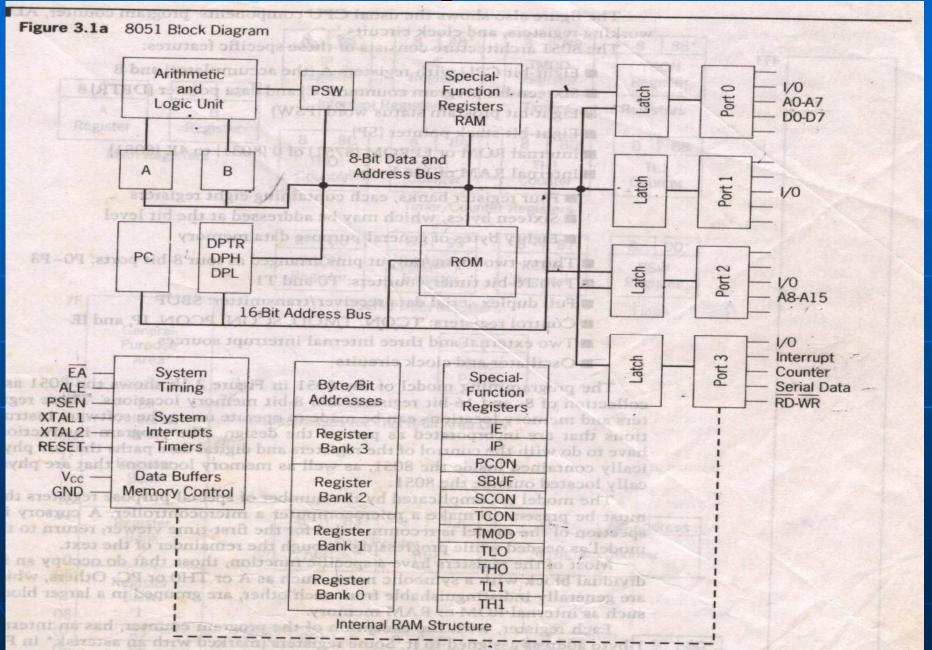

# Block Diagram of 8051

### 8051 Oscillator and Clock

- The oscillator is formed by the crystal, capacitors and an on-chip inverter.

- Circuitry that generates the clock pulses by which all internal operations are synchronized.

- Frequency- 1mHz to 16 mHz

- Minimum frequencies imply that some internal memories are dynamic and must always operate above a minimum frequency or data will be lost.

- The time to execute an instruction is found by

- Tinst = ( C x 12d ) / Crystal Frequency

- Where C number of machine cycles

# Program counter and Data Pointer

- PC does not have an internal address.

- Program instruction bytes are fetched from locations in memory that are addressed by the PC.

- DPTR register is made up of two 8 bit registers, named DPH and DPL, which are used to furnish memory addresses for internal and external code access and external data access.

- DPTR does not have a single internal address; DPH and DPL are each assigned an address.

# A and B CPU register

- 8051 contains 34 general purpose or working registers.

- Two of these registers A and B, hold results of many instructions, particularly math and logical operations, of the CPU.

- Other 32 register are arranged as part of internal RAM in four banks.

- 'A' register:

- Is most versatile of the two registers.

- It is used for many operations (arithmetical, logical and bit manipulations).

- Used for all data transfers between the 8051 and any external memory.

- 'B' register:

- Used with A register for multiplication and division operations

- No other function other than as a location where data may be stored.

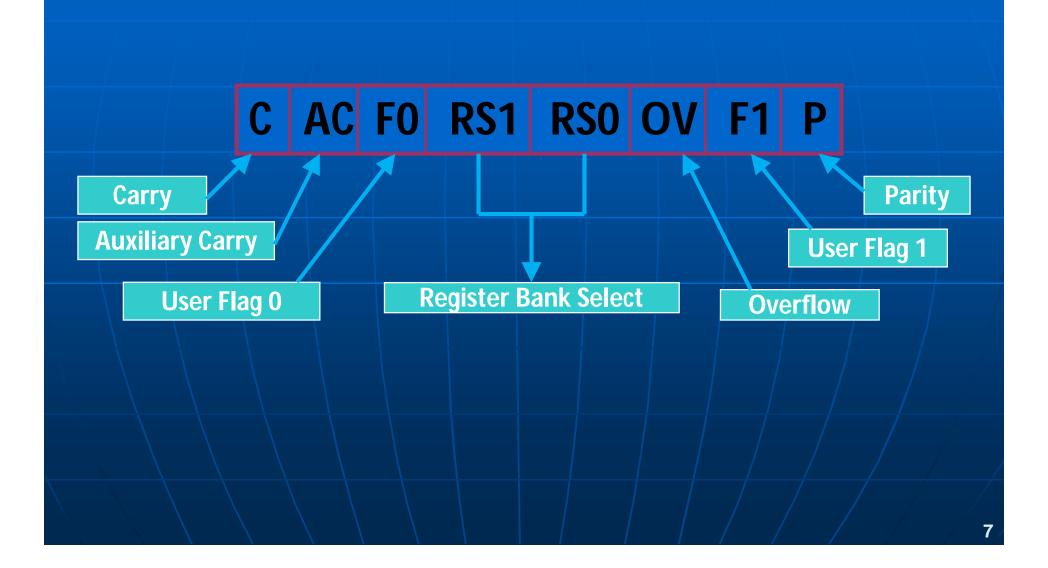

# Flags and Program Status Word [PSW]

# 128 Byte RAM

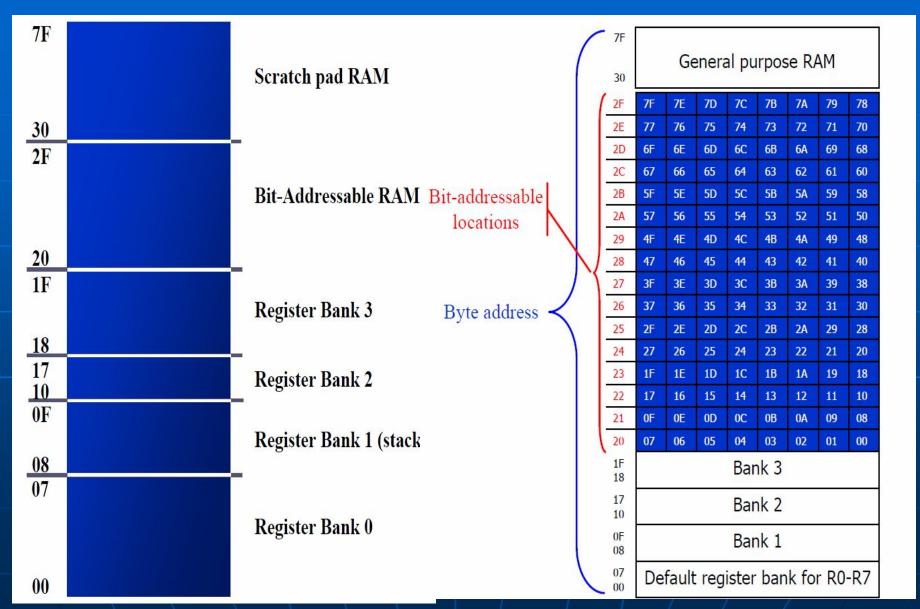

- There are 128 bytes of RAM in the 8051.

- Assigned addresses 00 to 7FH

- The 128 bytes are divided into 3 different groups as follows:

- 1. A total of **32 bytes** from locations 00 to 1F hex are set aside for *register banks*.

- 2. A total of **16 bytes** from locations 20H to 2FH are set aside for *bit-addressable* read/write memory.

- 3. A total of **80 bytes** from locations 30H to 7FH are used for read and write storage, called *scratch pad.*

General Purpose Area

BIT Addressable Area

Reg Bank 3

Reg Bank 2

Reg Bank 1

Reg Bank 0

### 8051 RAM with addresses

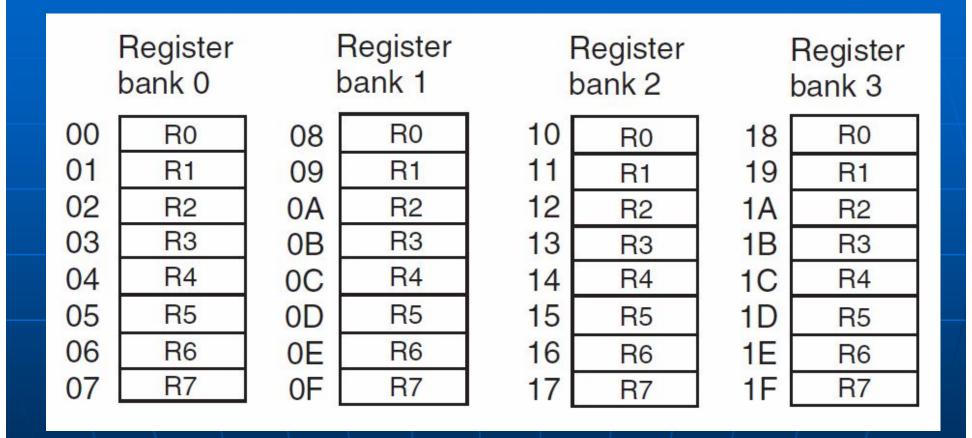

# 8051 Register Bank Structure

| Bank 3 —— | R0 | R1 | R2 | R3 | R4 | R5 | R6 | <b>R</b> 7 |

|-----------|----|----|----|----|----|----|----|------------|

| Bank 2 —— | R0 | R1 | R2 | R3 | R4 | R5 | R6 | <b>R</b> 7 |

| Bank 1 —— | R0 | R1 | R2 | R3 | R4 | R5 | R6 | R7         |

| Bank 0    | R0 | R1 | R2 | R3 | R4 | R5 | R6 | R7         |

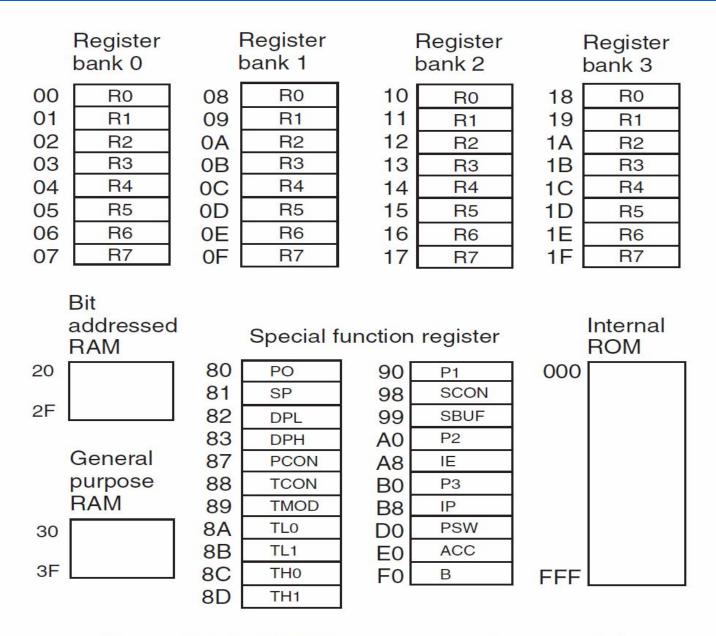

# 8051 Register Banks with address

Figure 3.1b 8051 Programming Model 8 88\* 8 B8\* 8 **A8**\* 8 89 **FFF** TCON IP ΙE TMOD Register Register Register Register 8 EO\* 8 FO\* **Timer Control Registers** Interrupt Registers A В Register Register 8 80 8 88 8 8D 8 8B Math Registers TLO TH1 TL1 THO Counter Counter Counter Counter Timer/Counter Registers D0\* 98\* 99 8 87 **SBUF PCON** PSW SCON Register Register Register Register Flags 7F Serial Data Registers General-8 81 Purpose Stack Area Pointer 30 2F 7F Bit Bit Addresses for This RAM Area Only Address Area 20 00 1F Register Bank 3 18 No Address 17 8 83 8 82 16 Register Bank Data Pointer Program Counter DPH DPL 10 OF Register Bank 1 08 07 R7 BO\* 80\* 8 90\* 8 A0\* 8 06 R6 Port 3 Port 2 Port 0 Port 1 Register 05 R5 Latch Latch Latch Latch Bank 04 R4 0 03 R3 02 R2 Number of Direct Byte Address \*Indicates Bit Addressable Bits 01 R1 00 RO 000 Internal Byte Internal ROM RAM Addresses

Figure C.3 80C51 programming model

# 8051 Stack and Stack pointer

- The stack is a section of RAM used by the CPU to store information temporarily.

- This information could be data or an address

- The register used to access the stack is called the SP (stack pointer) register

- The stack pointer in the 8051 is only 8 bit wide, which means that it can take value of 00 to FFH

- When the 8051 is powered up (i.e.,) reset, the SP register contains value 07

- RAM location 08 is the first location begin used for the stack by the 8051

# 8051 Stack and Stack pointer

- The storing of a CPU register in the stack is called a PUSH

- SP is pointing to the last used location of the stack

- As we push data onto the stack, the SP is incremented by one

- This is different from many microprocessors

- Loading the contents of the stack back into a CPU register is called a POP

- With every pop, the top byte of the stack is copied to the register specified by the instruction and the stack pointer is decremented once

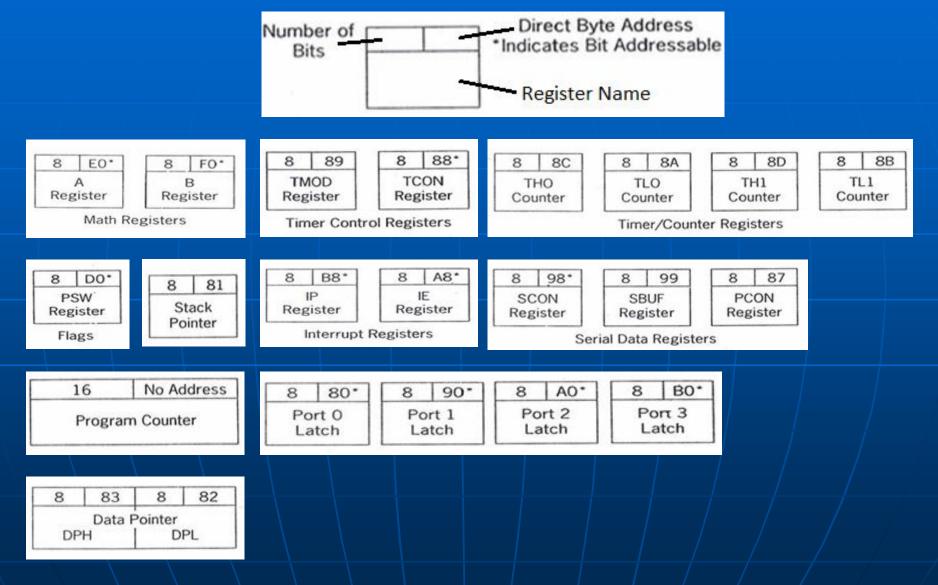

# Special Function Registers

- 80h to FFh are used for SFRs

- PC is not part of SFR.

| Name | Function                 | Name | Function                 |

|------|--------------------------|------|--------------------------|

| А    | Accumulator              | SBUF | Serial Port data buffer  |

| В    | Arithmetic               | SP   | Stack Pointer            |

| DPH  | Addressing Ext<br>Memory | TMOD | Timer/Counter mode cntrl |

| DPL  | Addressing Ext<br>Memory | TCON | Timer/Counter cntrl      |

| IE   | Interrupt enable         | TLO  | Timer0 lower byte        |

| IP   | Interrupt Priority       | THO  | Timer0 higher byte       |

| PO   | I/O Port Latch           | TL1  | Timer1 lower byte        |

| P1   | I/O Port Latch           | TH1  | Timer1 higher byte       |

| P2   | I/O Port Latch           |      |                          |

| P3   | I/O Port Latch           |      |                          |

| PCON | Power Control            |      |                          |

| PSW  | Pgm Status Word          |      |                          |

| SCON | Serial PortCntrl         |      |                          |

# Special Function Registers [SFR]