### Multiprocessor Configuration

By, S. Angel Deborah

# Multiprocessor configuration

- Multiprocessor means a multiple set of processors that executes instructions simultaneously.

- There are three basic multiprocessor configurations.

- Coprocessor configuration

- Closely coupled configuration

- Loosely coupled configuration

### **Coprocessor Configuration**

- A Coprocessor is a specially designed circuit on microprocessor chip which can perform the same task very quickly, which the microprocessor performs.

- It reduces the work load of the main processor.

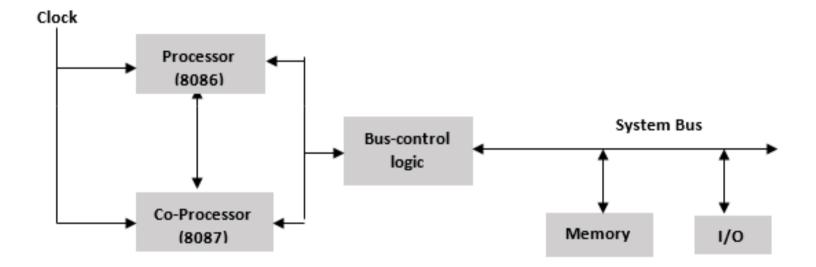

- The coprocessor shares the same memory, IO system, bus, control logic and clock generator.

- The coprocessor handles specialized tasks like mathematical calculations, graphical display on screen, etc.

- The 8086 and 8088 can perform most of the operations but their instruction set is not able to perform complex mathematical operations, so in these cases the microprocessor requires the math coprocessor like Intel 8087 math coprocessor, which can easily perform these operations very quickly.

### Block Diagram of Coprocessor Configuration

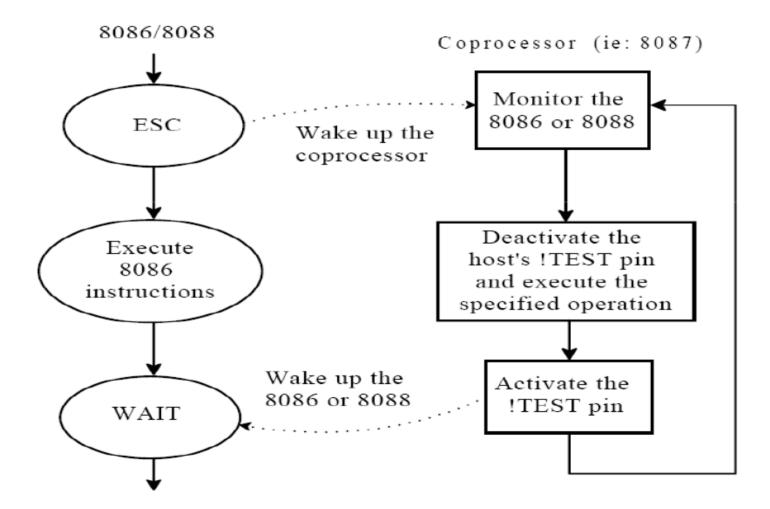

# How is the coprocessor and the processor connected?

- The coprocessor and the processor is connected via TEST, RQ-/GT- and  $QS_0 \& QS_1$  signals.

- The TEST signal is connected to BUSY pin of coprocessor and the remaining 3 pins are connected to the coprocessor's 3 pins of the same name.

- TEST signal takes care of the coprocessor's activity, i.e. the coprocessor is busy or idle.

- The RT-/GT-is used for bus arbitration.

- The coprocessor uses  $QS_0 \& QS_1$  to track the status of the queue of the host processor.

### **Closely Coupled Configuration**

- Closely coupled configuration is similar to the coprocessor configuration, i.e. both share the same memory, I/O system bus, control logic, and control generator with the host processor.

- However, the coprocessor and the host processor fetches and executes their own instructions. The system bus is controlled by the coprocessor and the host processor independently.

### Loosely Coupled Configuration

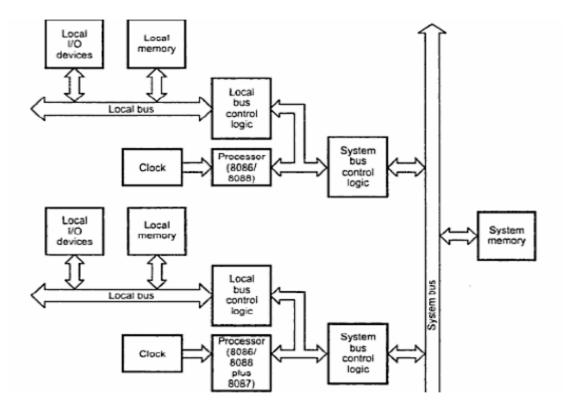

- Loosely coupled configuration consists of the number of modules of the microprocessor based systems, which are connected through a common system bus.

- Each module consists of their own clock generator, memory, I/O devices and are connected through a local bus.

- Clocks are of similar frequency, but asynchronous towards each other.

- Used for medium to large multiprocessor systems

- Each module is capable of being the bus master

- No direct connections between the modules.

- Each share the system bus and communicate through shared resources.

- Processor in their separate modules can simultaneously access their private subsystems through their local buses, and perform their local data references and instruction fetches independently.

- This results in improved degree of concurrent processing.

- Excellent for real time applications, as separate modules can be assigned specialized tasks.

### Loosely Coupled Configuration

### Loosely Coupled Configuration

#### Advantages:

- Having more than one processor results in increased efficiency.

- Each of the processors have their own local bus to access the local memory/I/O devices. This makes it easy to achieve parallel processing.

- The system structure is flexible, i.e. the failure of one module doesn't affect the whole system failure; faulty module can be replaced later.

### **Bus allocation Scheme**

#### Daisy Chaining:

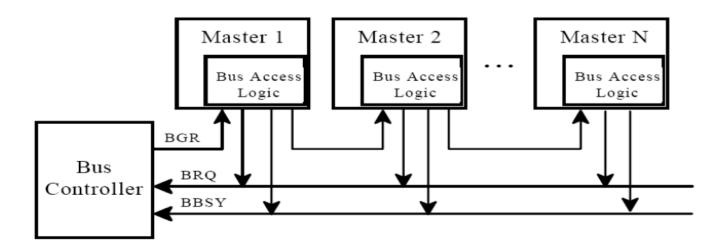

- Need a bus controller to monitor bus busy and bus request signals

- Sends a bus grant to a Masters; Each Master either keeps the service or passes it on

- Controller synchronizes the clocks Master releases the Bus Busy signal when finished

## **Daisy Chaining**

- Advantages

- It is simpler and cheaper method

- It requires the least number of lines and this number is independent of the number of masters in the system

- Disadvantages

- Propagation delay is proportional to the number of masters

- The priority of the master is fixed by its physical location

- Failure of one system causes the whole system to fail

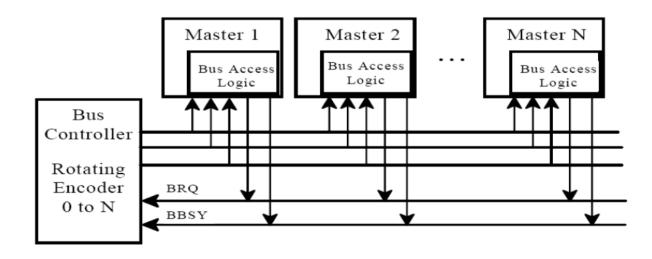

# Polling

- It uses a set of lines sufficient to address each module.

- In response to a bus request, the controller generates a sequence of module addresses.

- When a requesting module recognizes its address, it activates the busy line and begins to use the bus.

- The controller stops generating addresses when busy line is activated.

# Polling

- Advantages

- The priority can be changed by altering the polling sequence stored in the controller

- If one module fails entire system does not fail

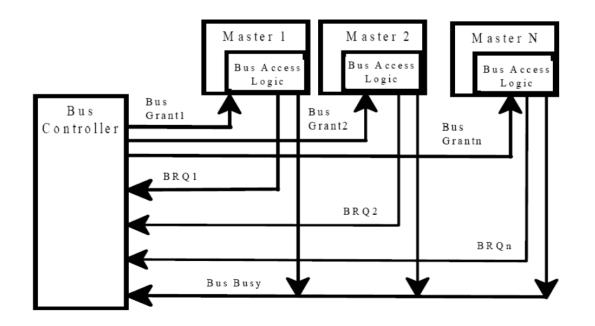

### Independent requesting

- Each module has a separate pair of bus request and bus grant lines.

- Each pair has a priority assigned to it.

- The controller includes a priority decoder, which selects the request with the highest priority assigned to it and returns the corresponding grant signal.

- The priority can be fixed priority or rotating priority.

### Independent requesting

- Advantages

- Due to separate pairs of bus request and bus grant signals, arbitration is fast and is independent of the number of masters in the system

- Disadvantages

- It requires more bus request and grant signals(2\*n signals for n modules).